不管中文或是英文都有很多文章在介紹這兩個理論的概念,在這裡是想用這兩種概念將程式寫的更容易維護和設計。

State Machine(SM)第一次看到這個名詞是我在研讀HMM的時後(有機會將這有趣的數學分享給大家),簡單來說就是狀態之間的轉移,數學上是以"機率"作為轉移依據,而在程式上是以"條件式"來決定。條件式在C語言裡不外乎使用 if / switch,

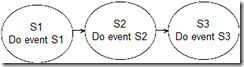

先來簡單的狀態序列<2>,配上常見的寫法我想會是~~

if (S=1) S = 2; do event S1

elseif (S=2) x = 3; do evnet S2

elseif (S=3) do event S3

或是用switch case…,想要讓狀態機多活一下,很直覺得就給它加個do while。這樣就大功告成了!?

小小狀態機或許這樣應該足夠了,但現在隨著硬體技術隨著<1>Moore定律的規範下不斷進步,其實軟體這裡也不會閒著,狀態機也是龐大的可怕,那這樣的寫法好maintain嗎? 我想這部分可以等到各位在工作時可以驗證一下,這裡是討論程式概念。

要怎麼做才直接且容易維護呢? 首先我們仔細想想,上述概念的寫法應該是這樣的SM。

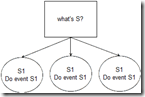

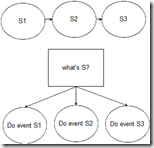

首先,我想引用<3><4>來解釋SM table的設計,這方法可以用來紀錄下一個狀態位置。

CurrentState = SMTable[CurrentState ] ;

很好,有了這個機制我們的架構就變成這樣了!

這是俗稱的多此一舉,脫褲子放屁? 問題出在哪呢? 因為每個狀態有屬於自己的函式要處理,如果能跟著CurrentState這index改變,那就兩全其美了。所以就有function point<5-7>存在的必要性。

此外,要寫好貼切的function point,我想宣告的問題可是非常重要,如#define, typedef, 宣告型態<8>...

這是我簡單寫一個上面所形容的狀態機(source code)分享給各位,希望能讓各位產生一絲絲的共鳴。

<Reference>

<1>http://en.wikipedia.org/wiki/Moore's_law

<2>http://www.swarthmore.edu/NatSci/echeeve1/Class/e15/E15Lab2/CStateMachines/CStateMachines.html

<3>http://www.conman.org/projects/essays/states.html

<4>http://johnsantic.com/comp/state.html

<6>http://stackoverflow.com/questions/133214/is-there-a-typical-state-machine-implementation-pattern

No comments:

Post a Comment